The Internet of Things (IoT) is a paradigm shift in technology. Billions of devices are now connected worldwide, generating huge amounts of data. The cost of transporting all this data to cloud infrastructure and processing the data in the cloud can be prohibitive, leading to cost overruns and failure of many IoT solutions. Edge Of Net Computing allows data to be processed at source; only the much-reduced critical data or results need then be sent to cloud infrastructure, reducing transmission and processing costs. This can also have the added benefits of reduced latency, reduced total power consumption, and, with care, improved security.

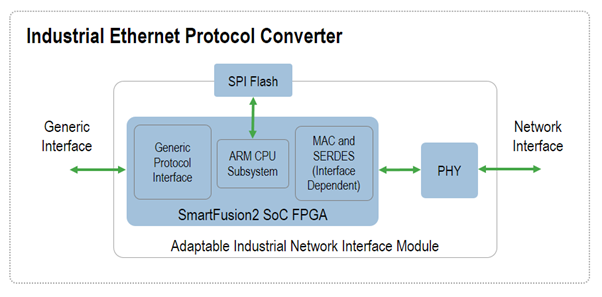

Additionally, in many industrial IoT applications there is a requirement to combine and process data from many disparate sources with different interface requirements. Many real systems require a complex mix of interfaces – multiple UARTs, Fieldbus, Ethercat, proprietary interfaces and so on, and this IO mix is beyond the interface capability of any processor. A good way to overcome this problem is to use an FPGA to consolidate and correlate all the inputs into a single format (in all probability Ethernet for IoT use) as shown in the diagram below.

The Microchip IGLOO2 family of FPGA devices is well matched with the requirement to combine multiple interface types into a single protocol. The FPGA fabric can be configured to expand IO as required to accommodate multiple different standard interfaces and proprietary interface standards. The SmartFusion2 FPGA adds an ARM Cortex M3 to the IGLOO2 FPGA fabric to enable Edge Of Net processing of the gathered data, helping to reduce the data burden to the cloud.

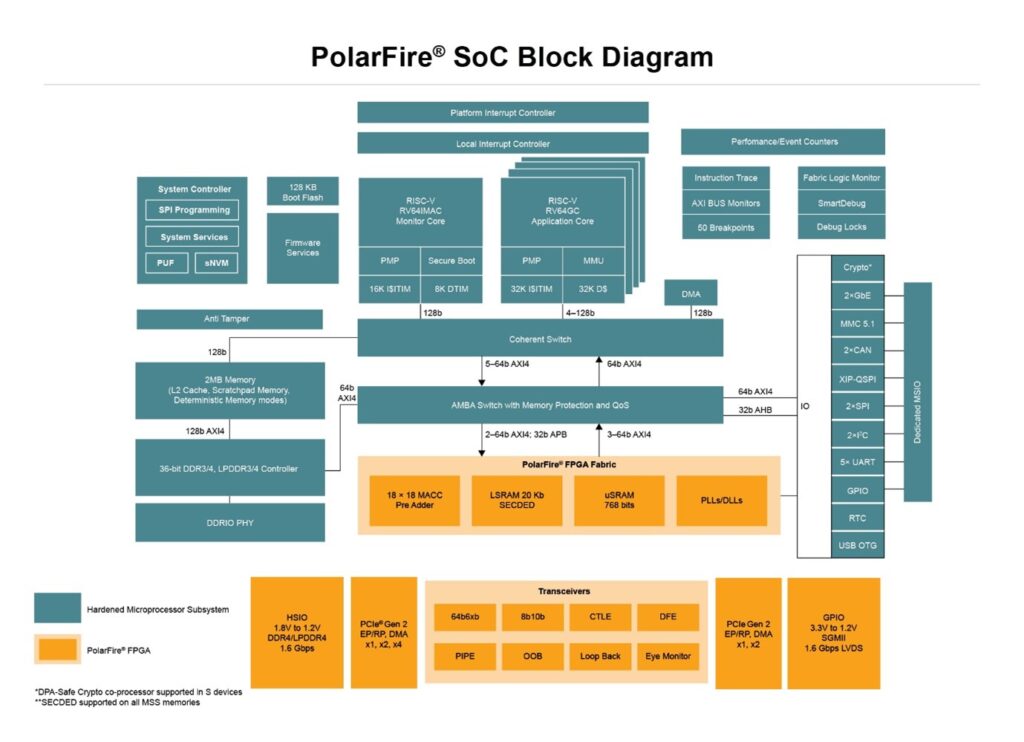

For video and other high data rate applications, the cost of streaming data to, and processing in, the cloud are extensive. The latency or response from the cloud can also be an issue in any time sensitive systems. The Microchip PolarFire and PolarFire SoC FPGA based devices are well suited to video and other high data rate Edge Of Net processing applications. They can handle HD and UHD video with SERDES transceivers operating up to 12.7Ghz. Embedded maths blocks in the FPGA Fabric enable the DSP and Maths functions in FPGA hardware to complete a wide range of image processing functions. DDR4 interfaces enable the handling of large local data store, such as Frame buffers for video analysis. The PolarFire SoC devices incorporate deterministic coherent 64-bit multi-core RISC-V real time Linux capable CPUs alongside the FPGA fabric for compute-intensive applications.

For more information about the Microchip FPGA devices please refer to our product webpages or